インテルアーキテクチャーのメモリ管理機構は、セグメント方式とページング方式の2つが存在します。セグメント方式は無効にすることは出来ませんが、ページング方式はCR0のPG bitを操作することにより、ON/OFFを切り替える事が出来ます。

インテルアーキテクチャーのメモリ管理機構は、セグメント方式とページング方式の2つが存在します。セグメント方式は無効にすることは出来ませんが、ページング方式はCR0のPG bitを操作することにより、ON/OFFを切り替える事が出来ます。

ページングが有効になっているときに、リニア・アドレスを物理アドレスに変換するために使用する情報は、次のデータ構造に入っている。

これらのテーブルによって、通常の32 ビット物理アドレス指定が使用されているときには4Kバイトまたは4M バイトのページ、また拡張(36 ビット) 物理アドレス指定が使用されているときには4K バイト、2M バイトまたは4M バイトのページにアクセスできるようになる。

ページング制御フラグの設定から得られるページ・サイズと物理アドレス・サイズを示す。

| CR0 PG Flag |

CR4 PAE Flag |

CR4 PSE Flag |

PDE PS Flag |

Page Size | 物理アドレス |

|---|---|---|---|---|---|

| 0 | - | - | - | - | ページングは無効 |

| 1 | 0 | 0 | - | 4Kbyte | 32bit |

| 1 | 0 | 1 | 0 | 4Kbyte | 32bit |

| 1 | 0 | 1 | 1 | 4Mbyte | 32bit |

| 1 | 1 | - | 0 | 4Kbyte | 36bit |

| 1 | 1 | - | 1 | 2Mbyte | 36bit |

各ページ・ディレクトリ・エントリには、PS(ページ・サイズ)フラグが含まれる。PSフラグは、エントリがページ・テーブルを指し、テーブルのエントリが4K バイト・ページを指すか(PS を0 に設定)、またはページ・ディレクトリ・エントリが4M バイトまたは2Mバイトのページを直接に指すか(PSEまたはPAEを1にセットし、PSを1にセット)を指定する。

ページ・ディレクトリのエントリはページ・テーブルを指し、ページ・テーブルのエントリは物理メモリのページを指している。このページング方式を使用して、220 ページまでアドレス指定することができ、これは232 バイト(4G バイト) のリニア・アドレス空間を占める。

さまざまなテーブル・エントリを選択するため、リニア・アドレスは次の3 つのセクションに分割される。

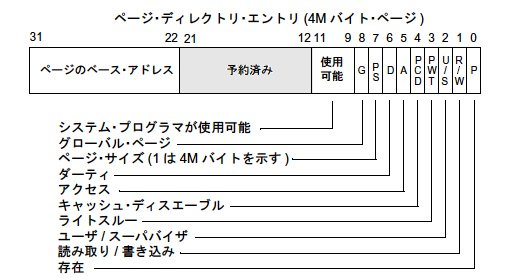

ページ・ディレクトリのエントリは、物理メモリ内の4M Byte Pageを指す。このページング方式を使用して1024 までのページを4G Byte リニア・アドレス空間にマッピングすることができる。

4M byteのページ・サイズを選択するには、制御レジスタCR4のPSE フラグをセットし、ページ・ディレクトリ・エントリのページ・サイズ(PS)フラグをセットする。これらのフラグをセットすると、リニア・アドレスは次の2つのセクションに分割される。

ページ・ディレクトリの物理アドレスは、CR3(ページ・ディレクトリ・ベース・レジスタまたはPDBR ともいう)に格納される。

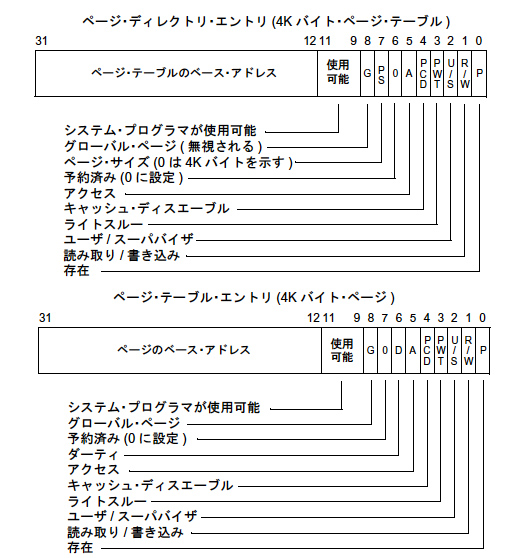

4K byte ページと32bit物理アドレスを使用しているときのページ・ディレクトリ・エントリとページ・テーブル・エントリは次のようになる。

4M byte ページと32bit 物理アドレスを使用しているときのページ・ディレクトリ・エントリは次のようになる。

PDEとPTEの内容は、次のようになる

| bit | FLAG | 意味 | 詳細 |

|---|---|---|---|

| 0 | P | P Flag |

エントリによって指されているページまたはページ・テーブルが物理メモリに現在ロードされているかどうかを示す。 このフラグがセットされていると、ページは物理メモリにあり、アドレス変換が行われる。クリアされていると、ページはメモリにはなく、プロセッサがページにアクセスしようとすると、ページ・フォルト例外(#PF) が発生する。 |

| 1 | R/W | Read/Write Flag |

ページまたは( ページ・テーブルを指しているページ・ディレクトリ・エントリの場合には) ページのグループの読み取り/ 書き込み特権を指定する。 このフラグがクリアされていると、ページは読み取り専用であり、セットされていると、ページの読み取りと書き込みを行うことができる。 |

| 2 | U/S | User Supervisor Flag |

ページまたは( ページ・テーブルを指しているページ・ディレクトリ・エントリの場合には) ページのグループのユーザ/ スーパバイザ特権を指定する。 このフラグがクリアされていると、ページにはスーパバイザ特権レベルが割り当てられている。 セットされていると、ページにはユーザ特権レベルが割り当てられている。 |

| 3 | PWT | Page Write Through Flag |

個別ページまたはページ・テーブルのキャッシュ方式をライトスルーにするかライトバックにするかを制御する。 PWT フラグがセットされていると、ライトスルー・キャッシングが関連するページまたはページ・テーブルに対してイネーブルになり、クリアされていると、ライトバック・キャッシングが関連するページまたはページ・テーブルに対してイネーブルになる。 |

| 4 | PCD | Page Cache Disable Flag |

個別ページまたはページ・テーブルのキャッシングを制御する。 PCD フラグがセットされていると、関連するページまたはページ・テーブルのキャッシングは禁止される。 クリアされていると、ページまたはページ・テーブルをキャッシュすることができる。 このフラグは、メモリ・マップドI/O ポートを含むページまたはキャッシングによる性能上の利益がないページに対してキャッシングをディスエーブルにすることができる。 |

| 5 | A | Access Flag |

セットされていると、ページまたはページ・テーブルがすでにアクセス(読み取りまたは書き込み)されたかどうかを示す。 このフラグは、「スティッキー」なフラグであり、これは、プロセッサはセットしてしまうと暗黙のうちにはクリアしないことを意味している。ソフトウェアだけがこのフラグをクリアすることができる。 OSがメモリが足りなくなった時に、ページアウトするページを選択するときに使用する。 |

| 6 | D | Dirty Flag |

セットされていると、ページが書き込まれたかどうかを示す。( このフラグは、ページ・テーブルを指しているページ・ディレクトリ・エントリでは使用されない。) メモリ管理ソフトウェアは、一般的にページが最初に物理メモリにロードされたときにこのフラグをクリアする。 その後、プロセッサは、ページが初めて書き込み操作のためにアクセスされたときにこのフラグをセットする。 このフラグは、「スティッキー」であり、これは、プロセッサはセットしてしまうと暗黙のうちにはクリアしないことを意味している。ソフトウェアだけがこのフラグをクリアすることができる。 |

| 7 | PS | Page Size Flag |

ページ・サイズを決定する。このフラグは、ページ・ディレクトリ・エントリだけで使用される。このフラグがクリアされていると、ページ・サイズは4K バイトであり、ページ・ディレクトリ・エントリはページ・テーブルを指す。 セットされていると、ページ・サイズは、通常の32 ビットのアドレス指定では4Mバイト( および拡張物理アドレス指定がイネーブルになっている場合は2M バイト) であり、ページ・ディレクトリ・エントリはページを指す。 ページ・ディレクトリ・エントリがページ・テーブルを指している場合は、そのページ・テーブルに関連するすべてのページは、4K バイト・ページになる。 |

| 8 | G | Global Flag |

セットされていると、グローバル・ページを示す。 ページがグローバルとマークされ、CR4 のページ・グローバル・イネーブル(PGE) フラグがセットされていると、そのページのページ・テーブル・エントリまたはページ・ディレクトリ・エントリは、CR3 がロードされるかまたはタスク・スイッチが発生してもTLB で無効化されない。 このフラグは、( カーネルやその他のオペレーティング・システムまたはエグゼクティブのコードを含むページなど) 頻繁に使用されるページがTLB からフラッシュされるのを防ぐために用意されたものである。ソフトウェアだけがこのフラグをセットまたはクリアすることができる。 ページ・テーブルを指しているページ・ディレクトリ・エントリの場合には、このフラグは無視され、ページのグローバル特性がページ・テーブル・エントリに設定される。 |

| 9-11 | - | OS予約 | OS用に、自由に使用が可能。 |

| 12-31 | - | ページのベース・アドレス |

(4K バイト・ページ用のページ・テーブル・エントリ) 4K バイト・ページの先頭バイトの物理アドレスを指定する。このフィールドのビットは、物理アドレスの上位20 ビットと解釈され、ぞれがページのアライメントを強制的に4K バイト境界に合わせる。 (4K バイト・ページ・テーブル用のページ・ディレクトリ・エントリ) ページ・テーブルの先頭バイトの物理アドレスを指定する。このフィールドのビットは、物理アドレスの上位20 ビットと解釈され、それがページ・テーブルのアライメントを強制的に4K バイト境界に合わせる。 (4M バイト・ページ用のページ・ディレクトリ・エントリ) 4M バイト・ページの先頭バイトの物理アドレスを指定する。このフィールドのビット22 〜 31だけが使用される(PentiumR II プロセッサまでのインテル・アーキテクチャ・プロセッサでは、ビット12 〜 21 は予約されており、0 に設定しなければならない)。ベース・アドレス・ビットは、物理アドレスの上位10 ビットと解釈され、これが4Mバイト・ページのアライメントを強制的に4Mバイト境界に合わせる。 |

プロセッサは、直前に使用されたページ・ディレクトリ・エントリとページ・テーブル・エントリをトランスレーション・ルックアサイド・バッファ(TLB) というオンチップのキャッシュに記憶する。

ほとんどのページングは、TLB の内容を使用して行われる。メモリ内のページ・ディレクトリとページ・テーブルへのバス・サイクルは、要求されたページの変換情報がTLB に入っていないときだけに行われる。

オペレーティング・システムは、TLB の対応するエントリが次に参照されるときに更新できるように、そのエントリをただちに無効化しなければならない。ただし、36 ビット・アドレス指定を使用するために物理アドレス拡張(PAE) 機能が使用可能になっている場合は、ページング階層に新しいテーブルが1 つ追加される。この新しいテーブルは、ページ・ディレクトリ・ポインタ・テーブルと呼ばれる(3.8. 節「物理アドレス拡張」を参照)。このテーブルのエントリが( 他のページ・ディレクトリを指すために) 変更された場合は、CR3 への書き込みによってTLB を空にしなければならない。